学内研究組織（2024年度）

研究課題：「電動航空機用軽量マルチレベル変換器システムの開発」

## スイッチドキャパシタ式マルチレベルインバータ（SCMLI）の 高効率化に関する研究

Study of Improving Efficiency of Switched Capacitor Multilevel Inverters

岩田 明彦 (Akihiko Iwata)

### 1. はじめに

航空機や自動車の電動化などは CO<sub>2</sub> ガス排出量の削減の重要な手段である。それらに使用する電力変換回路の高効率化や軽量化は燃費の向上による CO<sub>2</sub> ガス排出削減に繋がる。従来のチョッパ+2 レベルインバータの構成では、チョッパ回路にインダクタが必要であり、また、インバータの出力側に平滑用のフィルタが設置される場合もある。それらはいずれも重量増加要因となる。一方で、スイッチドキャパシタマルチレベルインバータ（SCMLI）は、マルチレベル化により出力を疑似正弦波化できるのみならず、自己昇圧機能を持つ。そのため昇圧用のインダクタや出力フィルタが不要となり、軽量化が期待できる。しかし、従来の SCMLI[1],[2]はキャパシタへ充電する時の電力消費が大きく、効率が低いという課題がある。本研究では SCMLI の先行研究からトポロジーの動作原理、損失メカニズム、パワー素子消費電力、パワー素子耐圧などを検討し、効率の改善が図れる新方式 SCMLI 回路を提案する。

### 2. 従来の SCMLI 回路の課題

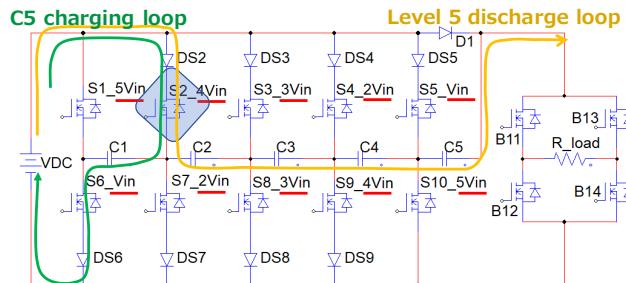

従来の SCMLI 回路[1]は電力変換効率が低いという課題を有している。また、絶縁された 2 つの電源が必要であるため、実用化のハードルが高い。図 1 に従来の SCMLI[1]の基本スイッチドキャパシタセル（SSC）のトポロジーを用いて構成された単電源 13 レベル SCMLI の構成を示す。赤点線で囲まれた箇所は基本のスイッチドキャパシタセルを示している。パワー素子名の後に、素子に印加される最大電圧（素子耐圧）を記載している。変換回路の総合計素子耐圧は 25Vin となる。図 1 の矢印はレベル 5 の場合の充放電経路を示す。矢印はそれぞれキャパシタの充電（緑）と放電（オレンジ色）経路である。表 1 は、ポジティブハーフサイクルにおける従来回路の各モード毎のキャパシタの充放電状況、スイッチのオンオフ状況及び各キャパシタの充放電時間比率（Charge time/Discharge time）を示している。C、D、(-) はそれぞれ充電、放電、デッドタイムを示す。レベル 0、1 では、キャパシタ C1～4 はデッドタイムモードである。レベル 2 の時に C4 はチャージモードになり、電源と C5 が直列接続され、2Vin が放電される。レベル 3 の時に C3 はチャージモードになり、電源と C4、C5 が直列接続され、3Vin が放電される。レベル 4～6 も同様な動作をする。図 1 の充放電経路をも見ると、充電経路と放電経路が共通化されている。この共通化された構成が、充放電時間比率を下げている原因となる。

表1のキャパシタの充放電時間比率のC<sub>1</sub>~C<sub>5</sub>の平均値は約0.324と低く、最も高いC<sub>1</sub>においても約0.76に留まっている。つまり、放電期間に対して充電時間が大幅に少ない。充電時間が短い場合、所定の電荷量を充電するための平均的な電流が増加せざるを得ず、結果的に充電ロスが増加する。従来の構成ではこの充電ロスが効率低下の要因となっており、文献[1]での実験効率は91%に留まる。

**Fig. 1 The circuit of the conventional SCMLI of 13 level, Arrows show current flows at output level 5.**

**Table 1 Switch and capacitor states for conventional 13-Level SCMLI in positive half-cycle.**

| Level            | On-Switches | Capacitor status |      |      |      |      |

|------------------|-------------|------------------|------|------|------|------|

|                  |             | C_1              | C_2  | C_3  | C_4  | C_5  |

| 6                | 1 12 13     | D                | D    | D    | D    | D    |

| 5                | 2 6 12 13   | C                | D    | D    | D    | D    |

| 4                | 3 7 12 13   | -                | C    | D    | D    | D    |

| 3                | 4 8 12 13   | -                | -    | C    | D    | D    |

| 2                | 5 9 12 13   | -                | -    | -    | C    | D    |

| 1                | 10 12 13    | -                | -    | -    | -    | C    |

| 0                | 10          | -                | -    | -    | -    | C    |

| Charge/Discharge |             | 0.76             | 0.31 | 0.20 | 0.16 | 0.19 |

### 3. キャパシタの充電時間と損失の関係

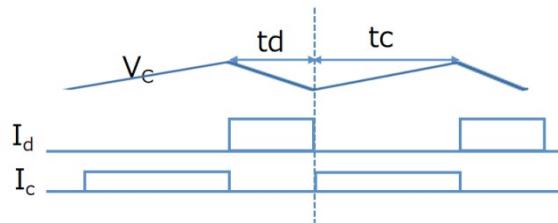

**Fig. 2 Diagram of the charging and discharging time and current for equivalent circuit of the SC basic cell.**

**Fig. 3 Equivalent circuit of charging and discharging for the SC basic cell in the SCMLI circuit.**

図 2 に SC セル等価回路の充放電時間と充放電電流のイメージ図を示す。図 3 は SCMLI 回路の SC セルの等価回路を示している。キャパシタンス C が十分に大きければ、図 2 に示したように、充電電流  $I_c$ 、放電電流  $I_d$  は一定と考えられる。充電抵抗  $R_c$  で消費した電力量  $W_{loss}$  は以下となる。

$$W_{loss} = [I_c]^2 \times R_c \times t_c \quad (1)$$

放電時の電荷量を  $Q$  とする。 $I=Q/t$  を式(1)に代入すると  $W_{loss}$  は以下となる。

$$W_{loss} = Q^2 / t_c \times R_c \quad (2)$$

式(2)を見ると、充電時間  $t_c$  が上がれば、 $W_{loss}$  は下がることがわかる。

#### 4. 提案の SCMLI 回路

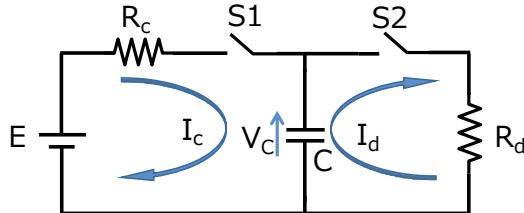

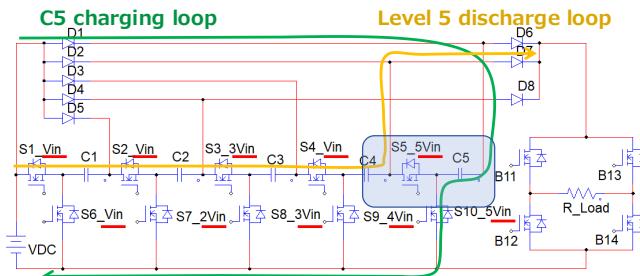

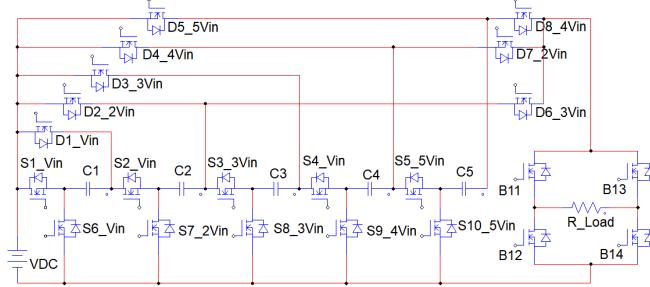

**Fig. 4 Proposed 13-Level SCMLI structure. Arrows show current flows at output level 5.**

**Table 2 Switch and capacitor states for proposed 13-Level SCMLI in positive half-cycle.**

**Level    On-Switches    Capacitor status**

| Level            | On-Switches      | Capacitor status |      |      |      |      |

|------------------|------------------|------------------|------|------|------|------|

|                  |                  | C1               | C2   | C3   | C4   | C5   |

| 6                | 1 2 3 4 5 12 13  | D                | D    | D    | D    | D    |

| 5                | 1 2 3 4 10 12 13 | D                | D    | D    | D    | C    |

| 4                | 3 4 5 6 7 12 13  | C                | C    | D    | D    | D    |

| 3                | 1 2 8 9 10 12 13 | D                | D    | C    | C    | C    |

| 2                | 5 6 7 8 9 12 13  | C                | C    | C    | C    | D    |

| 1                | 6 7 8 9 10 12 13 | C                | C    | C    | C    | C    |

| 0                | 6 7 8 9 10       | C                | C    | C    | C    | C    |

| Charge/Discharge |                  | 0.72             | 0.72 | 0.66 | 0.66 | 0.93 |

図 4 は提案する SCMLI の回路構成を示している。ここではこの回路を提案 1 方式と呼ぶ。提案 1 回路は、負荷への放電経路に複数の素子を直列に有するものの充電経路と放電経路を完全に切り分けた回路構造を持っている。これは結果的に、キャパシタの充放電時間比率を高めることにつながる。赤点線で囲まれた箇所は提案回路の基本 SSC セルを示す。パワー素子名の後に、図 1 と同様に印加される最大電圧（素子耐圧）を記載している。提案 1 方式の回路総合計素子耐圧は 14Vin となり、従来比 0.56 倍である。また、表 2 に各モードのスイッチの状態および各キャパシタの充放電の状況を示している。いずれのキャパシタにもスイッチが直列に接続されており、放電経路では従来方式よりも多くスイッチを経由する。しかし、表 2 から分かるように、提案方式の回路では、どのキャパシタにおいてデッドタイムモードがなく、キャパシタの充放電時間比率の C\_1~C\_5 の平均値は約 0.735 を確保できる。その中で充放電比率の最も高い C\_5 は約 0.93 に達している。このように提案 1 方式は従来方式に比べて充電期間が大幅に増加していることがわかる。提案 1 方式は負荷への電流経路の通過素子数が増加するものの、キャパシタの充電時のロス削減を狙っている。一般には、通過素子数が増加すればジュール損が増加するが、提案方式では素子の耐圧合計が従来比の 0.56 倍であるため、よりオン抵抗の小さい素子を選定ができる。その結果、ジュール損の増加を最小限に抑えることが可能である。

## 5. 試作機における検証結果

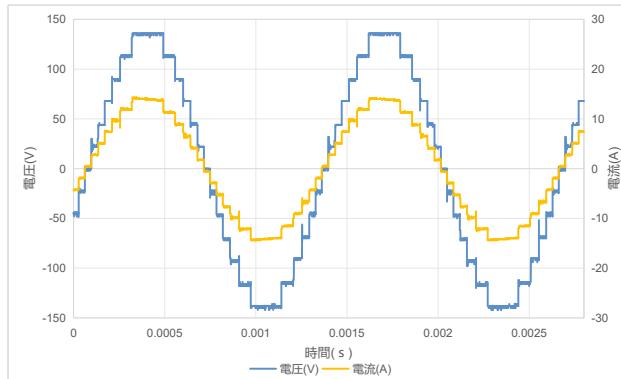

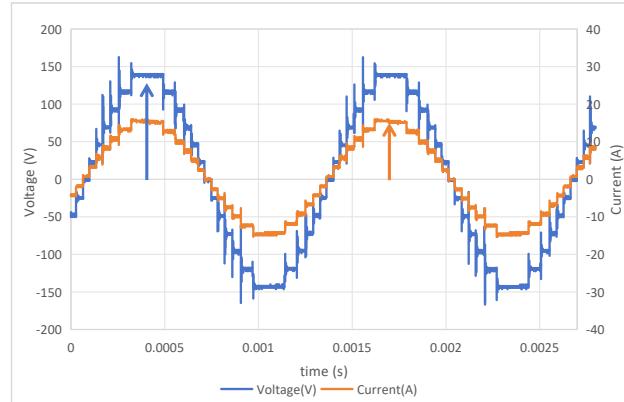

Fig. 5 Output waveform of the prototype circuit for the proposed SCMLI.

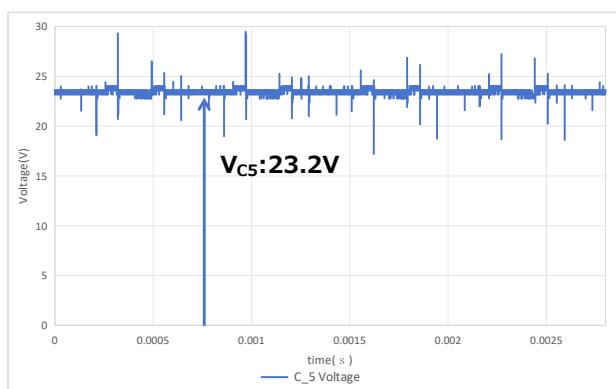

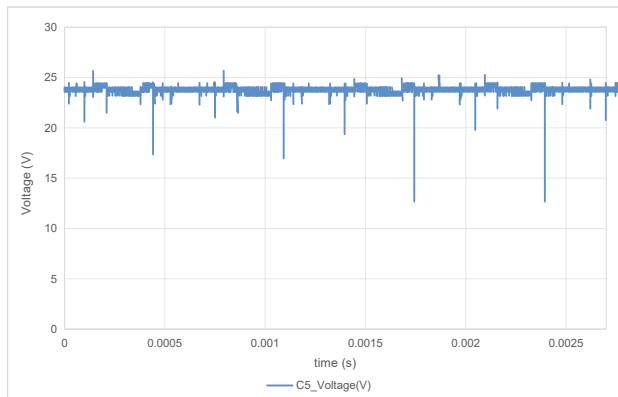

Fig. 6 Voltage waveform of capacitor C5 in the proposed SCMLI circuit.

実験条件は電源電圧 24V、抵抗負荷  $9.4\Omega$ 、周波数 800Hz、ダイオード(型番:40U300CT)降圧 0.84V、MOSFET\_1 オン抵抗  $1.9\text{m}\Omega$  (型番:IRLB3036PBF)、MOSFET\_2 オン抵抗  $10.9\text{m}\Omega$  (型番:SUP90100E) である。S1～S10 のパワー素子について、素子耐圧が  $V_{in}$  の場合は MOSFET\_1 を使用する。素子耐圧が  $2\sim 3V_{in}$  の場合は、MOSFET\_1 を 2 個直列接続して使用し、素子耐圧が  $4\sim 5V_{in}$  の場合は MOSFET\_2 を使用する。後述する整流ダイオードを MOSFET に置き換えた提案 2 方式において、D1 のパワー素子は MOSFET\_1 を使用し、D2～D8 のパワーは MOSFET\_2 を使用する。

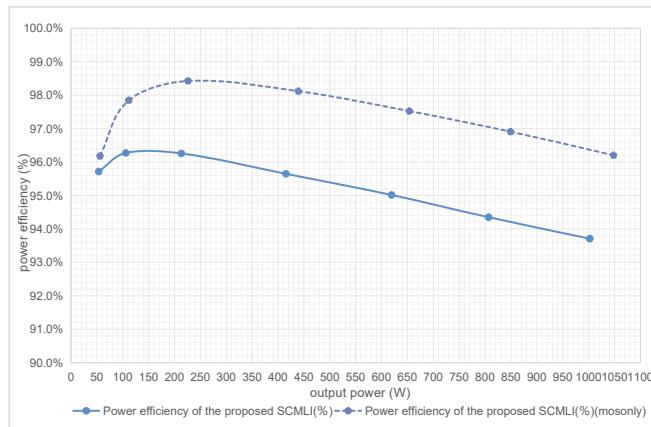

図 5 に提案 1 方式の出力電圧と電流グラフを示す。図 6 にキャパシタ C\_5 の電圧波形を示す。充電時のダイオードの電圧降下 VF によりキャパシタ C\_5 の充電電圧が 23.2V になり、電源電圧の 24V に比べて低いものの、出力最大電圧 138V が得られている。図 12 から出力電力 106.1W で最大の変換効率 96.2% が得られていることが分かる。

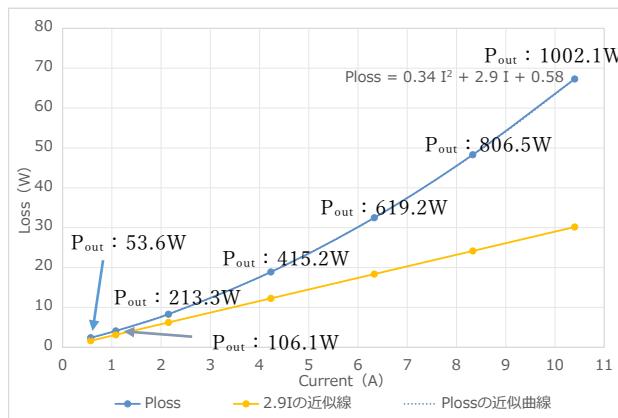

Fig. 7 Power loss graph of the proposed SCMLI circuit.

図 7 は提案 1 方式の電力損失グラフである。横軸と縦軸はそれぞれ出力電流と電力損失を示す。右上の式は電力損失グラフに基づいて試算した近似式である。オレンジ色の曲線は近似式の 1 乗項の損失グラフを示す。近似式の 1 乗項の損失はダイオードの電圧降下による損失だと推定できる。図 7 を見ると出力電力  $P_{out}$  が 1002.1W において、1 乗項による損失は全体損失の約 44.1% を占めることがわかる。

次に、ダイオードの電圧降下による損失を低減するために提案 2 方式を検討し実験検証を行った。図 8 に整流ダイオード D1～D8 を MOSFET に置き換えた提案 2 方式(MOSFET Only 提案 2 方式)を示す。パワー素子名の後に、素子に印加する最大電圧を記載している。図 9 に MOSFET Only 提案 2 方式の出力電圧と電流波形を示している。この条件では最大電圧 140V が得られている。図 12 から出力電力 226W で最大の変換効率 98.4% が得られていることが分かる。図 10 に MOSFET Only 回路形式のキャパシタ C\_5 の電圧波形を示す。キャパシタはほぼ電源電圧 24V に充電されている。

**Fig. 8 The proposed SCMLI circuit with the rectifier diode replaced by a MOSFET.**

**Fig. 9 Output waveform of the proposed SCMLI circuit with a diode replaced by a MOSFET.**

**Fig. 10 Voltage waveform of capacitor C5 in the proposed SCMLI circuit with a diode replaced by a MOSFET.**

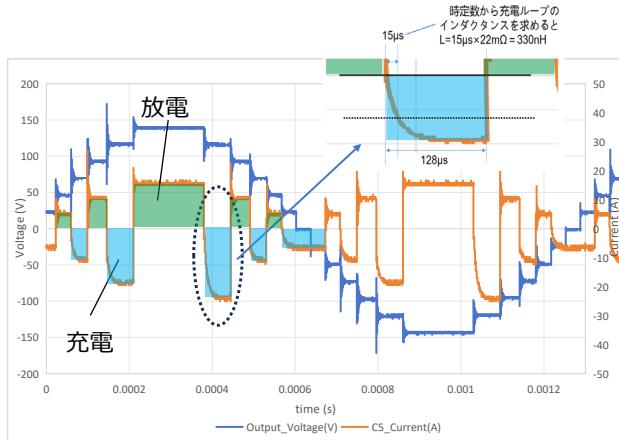

図 11 に出力電圧と C\_5 の電流波形を示す。緑色と青色で塗りつぶされた所はそれぞれ C\_5 の放電期間と充電期間を示す。図 11 から充電期間の電流波形は一次遅れ曲線になっていることが分かる。この一次遅れの立ち上がりは配線などの寄生インダクタンスによるものだと考えられる。図 11 の右上にレベル 5 のループの寄生インダクタンスを試算した。時定数からレベル 5 の充電ループのインダクタンスを求めるとき、この時の配線などによる寄生インダクタンスは約 330nH となった。充電経路の寄生インダクタンスによる過渡時間を考慮すれば、充電期間の電流はほぼ一定と推定できる。セクション 3 の損失

解析で電流の仮定と一致する。

**Fig. 11 Output voltage waveform and current waveform of C5 in the proposed SCMLI circuit with a diode replaced by a MOSFET.**

**Fig. 12 Power efficiency of the proposed SCMLI.**

図 12 に示したのは提案 1 方式および提案 2 方式の SCMLI 回路の変換効率グラフである。提案 1 方式の SCMLI 回路の効率変化グラフは実線に示す。MOSFET Only 提案 2 方式の効率変化グラフは点線に示す。図 12 を見ると、提案 1 方式と MOSFET Only 提案 2 方式の最大変換効率はそれぞれ 96.2% (Pout : 106.1W)、98.4% (Pout : 226.0W) を示した。最大出力電力において、それぞれ 93.7% (1002.1W)、96.2% (1048.0W) の変換効率を示した。文献 1 と 2 の実験検証による効率を黒いドットで図 12 にプロットした。文献 1 は出力電力 Pout260W で 91.06% の変換効率を得られている。文献 2 は出力電力 Pout226W で 92.1% の変換効率を得られている。提案回路を先行文献と比較すると、提案 1 方式と MOSFET Only 提案 2 方式は、文献 1 よりそれぞれ 4.9 と 7.3 ポイントアップが得られている。また、文献 2 よりそれぞれ 4.1 と 6.3 ポイントアップが得られている。先行文献 1、2 の実験検証変換効率に比べて提案の SCMLI 回路は 4 ポイント以上の効率アップ率が得られている。2 つの提案回路は優れた変換効率を示した。

## 6. まとめ

従来の SCMLI ではキャパシタの十分な充電時間を確保できないため、充電ロスが大きくなり効率が上がらないという課題がある。本研究では、キャパシタの平均充放電時間比率が 0.735 を確保できる SCMLI 回路を提案した。試作機における実験検証により、提案 1 方式の SCMLI 回路では最大変換効率 96.2% が実現できることを確認した。更に、ダイオードの電圧降下による損失を低減できる MOSFET Only 提案 2 方式の実験検証を行った。提案回路の MOSFET Only 回路形式では最大変換効率 98.4% が実現できることを確認した。また、先行文献の SCMLI 回路の実験効率と見比べて、提案の SCMLI 回路は優れた変換効率を示した。

## 文 献

- [1] Tapas Roy ,and Pradip Kumar Sadhu,“A Step-Up Multilevel Inverter Topology Using Novel Switched Capacitor Converters With Reduced Components”,IEEE Trans. Ind. Electron., Vol. 68, No. 1,pp. 236-247 Jan. 2021.

- [2] T. Roy, P. K. Sadhu, and A. Dasgupta, “Cross-switched multilevel inverter using novel switched capacitor converters,” IEEE Trans. Ind. Electron., vol. 66, no. 11, pp. 8521-8532, Nov. 2019.